半導(dǎo)體 | 晶圓制造工藝基礎(chǔ)知識(shí)

在具體晶圓制造之前,先對晶圓、芯片及其術(shù)語做一個(gè)大致的介紹會(huì)有助于我們的理解:

晶粒(chip、die)、器件(device)、電路(circuit)、微芯片(microchip)或條碼(bar):下圖中可以看到,很多四邊形都聚集在圓形晶圓上,所有這些名詞指的都是這些四邊形代表的微芯片圖形。將測試合格的die切割下來,做封裝后就成為芯片,一個(gè)芯片封裝一個(gè)die稱為單封,封裝兩個(gè)或兩個(gè)以上的die稱為合封。

劃片線(scribe line、saw line)或街區(qū)(street、avenue):看上去各個(gè)晶粒像是粘在一起,但實(shí)際上晶粒與晶粒之間具有一定的間隙,該間隙稱為劃片線。在晶粒和晶粒之間設(shè)置分割線的是為了在晶圓加工完成后將這些晶粒一個(gè)個(gè)割斷,然后組裝成芯片。劃片線通常是空白的,但有些公司在間隔區(qū)內(nèi)放置對準(zhǔn)標(biāo)記,或測試的結(jié)構(gòu)。

工程實(shí)驗(yàn)片(engineering die)和測試晶粒(test die):這些晶粒與正式晶粒或電路晶粒不同。它包括特殊的器件和電路模塊用于晶圓生產(chǎn)工藝的電性測試;

邊緣晶粒(edge die):在晶圓邊上的一些掩膜殘缺不全的晶粒而產(chǎn)生的面積損耗。由于單個(gè)晶粒尺寸增大而造成的更多邊緣浪費(fèi)會(huì)由采用更大直徑晶圓所彌補(bǔ)。推動(dòng)半導(dǎo)體工業(yè)向更大直徑晶圓發(fā)展的動(dòng)力之一就是為了減少邊緣晶粒所占的面積。

晶圓的晶面(wafer crystal plane):圖中的剖面標(biāo)示了器件下面的晶格構(gòu)造,此圖中顯示的器件邊緣與晶格構(gòu)造的方向是確定的;

晶圓定位邊(wafer flats)/凹槽(notche):圖示的晶圓由主定位邊(major flat)和副定位邊(minor flat),表示這是一個(gè)P型<100>晶向的晶圓。300mm和450mm直徑的晶圓都是用凹槽作為晶格導(dǎo)向的標(biāo)識(shí),和定位邊晶圓相比,凹槽晶圓可以制造更多的晶粒,因此效率很高。

以一個(gè)中規(guī)模(MSI)/雙極型集成電路(IC)的顯微照片為例。(之所以選擇這個(gè)集成等級(jí),是為了照片上能顯示出電路的具體圖形。對于更高集成度的電路,它的元件非常小,以至于在整個(gè)芯片的顯微照片上無法辨認(rèn)。)下圖中芯片的特性是:

晶圓制造可分為前端工藝(Front end)和后端工藝(Back end)。前端工藝主要是制備晶體管,后端工藝為晶體管制備之后的多層布線工序。總體而言,前端是需要多次重復(fù)相同的工序進(jìn)行產(chǎn)品生產(chǎn)的方式,因此稱為“循環(huán)型工藝”。前端制程主要包括:清洗、氧化、光刻、刻蝕、離子注入和熱處理、成膜、平坦化(CMP,Chemical Mechanical Polishing,化學(xué)機(jī)械拋光)、中測,多次循環(huán)并把前段制程集成化。

我們知道在比人類的“指甲蓋”還小、像紙一樣薄的半導(dǎo)體芯片上有著細(xì)小的、數(shù)以“百萬計(jì)”的層 (layer)。就像高樓大廈一樣高而堅(jiān)固地堆疊起來, 構(gòu)成復(fù)雜的結(jié)構(gòu)。薄膜工藝(layering)是在晶圓表面形成薄膜的加工工藝。這些薄膜可以是絕緣體、半導(dǎo)體或?qū)w。它們由不同的材料,并使用多種工藝生長或淀積而成。這些薄膜起到電路之間的分隔、連接和保護(hù)作用,成膜指的就是生成這種薄膜的過程。通用的淀積技術(shù)是物理氣相淀積(PVD),化學(xué)氣相淀積(CVD)、蒸發(fā)和濺射、分子束、外延生長、分子束外延和原子層淀積(ALD)。使用電鍍在高密度集成電路上淀積金屬化層。

圖形化工藝是將一系列生產(chǎn)步驟將晶圓表面薄膜的特定部分去除的工藝。在此之后,晶圓表面會(huì)留下帶有微圖形(pattern)結(jié)構(gòu)的薄膜。被除去的部分可能形狀是薄膜內(nèi)的孔或是殘留的島狀部分。

圖形化工藝是所有工藝中最關(guān)鍵的,圖形化工藝確定了器件的關(guān)鍵尺寸。圖形化工藝過程中的錯(cuò)誤可能造成圖形歪曲或套準(zhǔn)不好,最終影響器件性能。圖形化工藝在現(xiàn)代晶圓中要完成30層或更多,制程中的污染物會(huì)造成缺陷,缺陷也會(huì)影響器件性能。

電路版圖設(shè)計(jì):電路的工作運(yùn)行與很多因素相關(guān),包括材料電阻率,材料物理特性和元件的物理尺寸。另外的因素是各個(gè)元件之間的相對定位關(guān)系。所有這些要考慮的因素決定了元件、器件、電路的物理布局和尺寸。線路圖設(shè)計(jì)使用專用的軟件將電路元件轉(zhuǎn)為具體的圖形和尺寸。制造集成電路和蓋樓房同樣需要一層一層的建,因此必須將電路的復(fù)合圖分解為每層的設(shè)計(jì)圖,每層的圖形是數(shù)字化的(數(shù)字化使圖形轉(zhuǎn)換為數(shù)據(jù)庫)并由計(jì)算機(jī)處理的X-Y坐標(biāo)的設(shè)計(jì)圖。

光刻母版和掩膜版:光刻工藝用于晶圓表面和內(nèi)部產(chǎn)生需要的圖形和尺寸。光刻母版是在玻璃或石英板的鍍薄膜鉻層上生成分層設(shè)計(jì)電路圖的復(fù)制圖。電子束曝光系統(tǒng)跳過母版或掩膜版,直接在晶圓上曝光。光刻母版和掩膜版由工廠單獨(dú)的部門制造或從外部供應(yīng)商購買,每個(gè)電路類型都有自己分別的光刻母版或掩膜版。

基本十步的圖形化工藝:

摻雜是將特定量的雜質(zhì)通過薄膜開口引入晶圓表層的工藝過程,其本質(zhì)是在晶圓上制作P、N結(jié)。它有兩種工藝方法:熱擴(kuò)散(thermal diffusion)和離子注入(ion implantation)。熱擴(kuò)散是在1000℃左右的高溫下發(fā)生的反應(yīng),氣態(tài)下的摻雜原子通過擴(kuò)散化學(xué)反應(yīng)遷移到暴露的晶圓表面,形成一層薄膜,在芯片應(yīng)用中,熱擴(kuò)散也稱為固態(tài)擴(kuò)散,因?yàn)榫A材料是固態(tài)的。擴(kuò)散摻雜是一個(gè)化反應(yīng)過程,由物理規(guī)律支配雜質(zhì)的擴(kuò)散運(yùn)動(dòng)。離子注入是一個(gè)物理過程,在離子源的一端,摻雜體原子被離子化(帶有一定的電荷),被電場加到超高速,穿過晶圓表面,注入到晶圓表層中。

熱處理是簡單的將晶圓加熱和冷卻來達(dá)到特定結(jié)果的制程。在熱處理的過程中,在晶圓上沒有增加或減去任何物質(zhì)。然而,工藝過程可能會(huì)在晶圓中或晶圓上面產(chǎn)生污染。

在離子注入制程后會(huì)有一個(gè)重要的熱處理。摻雜原子的注入所造成的晶圓損傷會(huì)被熱處理修復(fù),這被稱為退火(anneal),溫度在1000℃左右。金屬導(dǎo)線制成后為了確保良好的導(dǎo)電性,金屬會(huì)在450℃熱處理后與晶圓表面緊密熔合。熱處理的第三種重要用途是通過加熱在晶圓表面的光刻膠將溶劑蒸發(fā)掉,從而得到精確的圖形。

量/檢測是半導(dǎo)體制造重要的質(zhì)量檢查工藝,涉及膜厚、折射率、膜應(yīng)力等參數(shù)測量,以及各類表面缺陷檢測等,對硅片廠/晶圓廠保障產(chǎn)品良率、產(chǎn)品一致性、降低成本等至關(guān)重要。在品圓制造完成之后,接下來是一步非常重要的測試步驟:晶圓中測。這步測試是品圓生產(chǎn)過程的報(bào)告卡。在測試過程中,檢測每一個(gè)芯片的電性能和電路功能。品圓中測又稱為芯片分選(die sort)或電分選(electrical sort)。

參考文獻(xiàn):

內(nèi)容來源:編輯整理

全部評(píng)論(0條)

推薦閱讀

-

- 半導(dǎo)體 | 晶圓制造工藝基礎(chǔ)知識(shí)

- 集成電路元器件的關(guān)鍵

-

- 半導(dǎo)體 | 晶體生長和晶圓制備

- 芯片的根基

-

- 半導(dǎo)體行業(yè)的溫度控制解決方案(一):晶圓制造中的精準(zhǔn)溫控

- 和 LAUDA 一起,逐層揭開半導(dǎo)體制造的溫度密碼吧!

-

- 顯微白皮書 | 半導(dǎo)體/晶圓檢測指南

- 為什么要使用顯微鏡?在產(chǎn)品開發(fā)和生產(chǎn)過程中,對半導(dǎo)體元器件進(jìn)行詳細(xì)檢查,以確保IC芯片、顯示器及其他電子元器件的質(zhì)量與可靠性。

-

- 鎂伽晶圓切割工藝:微米間的"芯"突破,解鎖半導(dǎo)體制造的關(guān)鍵一環(huán)

- 微米級(jí)精度,納米級(jí)匠心

-

-

-

-

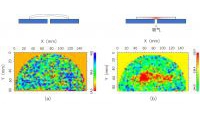

- 深入理解半導(dǎo)體晶圓形變對應(yīng)力的影響機(jī)制

- 晶圓應(yīng)力檢測是半導(dǎo)制造過程中極為重要的一環(huán),但并不是晶圓形變越大應(yīng)力就越大。R1系列晶圓級(jí)共焦拉曼光譜儀可以自動(dòng)聚焦跟蹤晶圓表面且進(jìn)行自動(dòng)化掃描,適用于大尺寸且有翹曲度的樣品,提供更全面的應(yīng)力檢測信息

-

- 半導(dǎo)體行業(yè)應(yīng)用專題 | 晶圓制造中CMP與刻蝕后清洗工序中關(guān)鍵物料的在線監(jiān)控方案

- 在刻蝕后清洗中,DSP+溶液中的H?SO?和HF濃度監(jiān)測對于控制清洗效果至關(guān)重要,過高或過低的酸濃度會(huì)影響金屬去除和氧化物清洗效率。

-

- 半導(dǎo)體 | 清洗工藝

- 據(jù)統(tǒng)計(jì),清洗工藝的次數(shù)占到了在整個(gè)芯片制造工藝步驟的三分之一,是芯片制造的重要環(huán)節(jié)。

-

- 半導(dǎo)體 | 氧化工藝

- 氧化過程的作用是在晶圓表面形成保護(hù)膜。它可以保護(hù)晶圓不受化學(xué)雜質(zhì)影響、避免漏電流進(jìn)入電路、預(yù)防離子植入過程中的擴(kuò)散以及防止晶圓在刻蝕時(shí)滑脫。

-

- 半導(dǎo)體 | 摻雜工藝

- 摻雜是控制半導(dǎo)體材料導(dǎo)電性、導(dǎo)電類型的重要步驟。

-

- 半導(dǎo)體 | 金屬化工藝

- 金屬化工藝是把各個(gè)元件連接到一起的材料工藝、連線過程。

-

- 半導(dǎo)體 | 刻蝕工藝

- 利用光刻工藝所形成的光刻膠作為掩膜來進(jìn)行的

-

- 晶圓級(jí)封裝技術(shù)是什么?

- 晶圓級(jí)封裝技術(shù)是什么?晶圓級(jí)封裝是指在將要制造集成電路的晶圓分離成單獨(dú)的電路之前,通過在每個(gè)電路周圍施加封裝來制造集成電路。由于在部件尺寸以及生產(chǎn)時(shí)間和成本方面的優(yōu)勢,該技術(shù)在集成電路行業(yè)中迅速流行起來。

-

- 什么是晶圓鍵合?

- 晶圓鍵合是用于制造微機(jī)電系統(tǒng)(MEMS),納米機(jī)電系統(tǒng)(NEMS)或光電或微電子物體的設(shè)備的過程。“晶圓”是一小片半導(dǎo)電材料,例如硅,用于制造電路和其他電子設(shè)備。

-

- 國產(chǎn)自研 | 晶圓級(jí)與超寬禁帶半導(dǎo)體光電測試系列產(chǎn)品

- 化合物半導(dǎo)體行業(yè)核心工具

①本文由儀器網(wǎng)入駐的作者或注冊的會(huì)員撰寫并發(fā)布,觀點(diǎn)僅代表作者本人,不代表儀器網(wǎng)立場。若內(nèi)容侵犯到您的合法權(quán)益,請及時(shí)告訴,我們立即通知作者,并馬上刪除。

②凡本網(wǎng)注明"來源:儀器網(wǎng)"的所有作品,版權(quán)均屬于儀器網(wǎng),轉(zhuǎn)載時(shí)須經(jīng)本網(wǎng)同意,并請注明儀器網(wǎng)(www.yosen.net.cn)。

③本網(wǎng)轉(zhuǎn)載并注明來源的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品來源,并自負(fù)版權(quán)等法律責(zé)任。

④若本站內(nèi)容侵犯到您的合法權(quán)益,請及時(shí)告訴,我們馬上修改或刪除。郵箱:hezou_yiqi

最新話題

最新文章

- 重塑金屬線材清洗流程,看潔盟超聲波清洗機(jī)如何助力產(chǎn)線“跑”起來!

- BeNano 180 Zeta Max檢測二氧化硅拋光液濃度

- 別讓"問題食品"成為考場絆腳石:食品安全檢測如何為學(xué)子護(hù)航?

- 【DeepSeek說顆粒知識(shí)】粒度分布的幾種表示方法?

- BT-1001智能粉體特性測試儀

- 寡核苷酸藥物純化“精”要:從雜質(zhì)特性到填料選型

- 想實(shí)現(xiàn)高精度表征納米金顆粒粒徑?這篇表征案例推薦給你

- 維生素D噴霧干燥機(jī)實(shí)驗(yàn)案例分享

- 鎂伽晶圓切割工藝:微米間的"芯"突破,解鎖半導(dǎo)體制造的關(guān)鍵一環(huán)

- 褪黑素新國標(biāo)來襲!為健康睡眠保駕護(hù)航!

作者榜

參與評(píng)論

登錄后參與評(píng)論